A Low-Noise Instrumentation Amplifier With Built-in Anti-Aliasing for Hall Sensors

An instrumentation amplifier is the first low-noise amplification stage of many sensor systems. Typical IA topologies for low-noise amplification are current feedback IA (CFIA) and capacitively coupled IA (CCIA).

A proposed prototype uses an In-the-Loop Sampling Amplifier (ILSA) as the core interface circuit for a Hall sensor front end. Both CFIA and CCIA designs are compatible with the in-the-loop sampling concept. The prototype uses a current feedback instrumentation amplifier (CCIA).

The ILSA architecture consists of a low-noise transconductance (LNT) in the forward path followed by a current-to-voltage integrator. Uniquely, a sample-and-hold (S&H) circuit is added at the end of the forward path within the analog feedback loop. This reasonably simple alteration introduces inherent anti-alias filtering into the system. The mixed-signal circuit is solved analytically to calculate the signal transfer function before sampling. Broad notches get created at multiples of the sampling frequency (fs). A Nyquist-rate analog-to-digital converter (ADC) digitizes each analog sample taken by the S&H block. The anti-aliasing filtering comes from the tight coupling of the analog sampling by S&H and digitization of ILSA output by ADC.

The Hall plate is a reliable and compact option for magnetic sensing. However, it is also known to produce large offsets. The offset and noise get translated to the edge of the Nyquist-ADC bandwidth by incorporating chopping and spinning in the ILSA architecture. They then get filtered out by the digital domain.

The residual or chopped offset ripples can still affect the dynamic range or cause amplifier saturation. A ripple reduction loop (RRL) can detect the offset ripple at the end of the readout chain and inject a compensation signal at the input of the amplifier. This helps in negating the offset from the readout chain before amplification.

In an innovative move, a digital RRL with a low-resolution DAC and corresponding quantization noise cancellation logic was employed. Such a digital variant synergizes splendidly with the inherent anti-alias filtering of the ILSA. The digital domain has several advantages, like low area, low power, and flexibility.

Furthermore, instead of a standard integrator/accumulator, a bilinear integrator is used as an RRL controller so that the RRL does not affect the DC gain of the overall system. Unlike analog implementations, the ideal DC gain of a digital integrator can achieve total removal of the offset ripple.

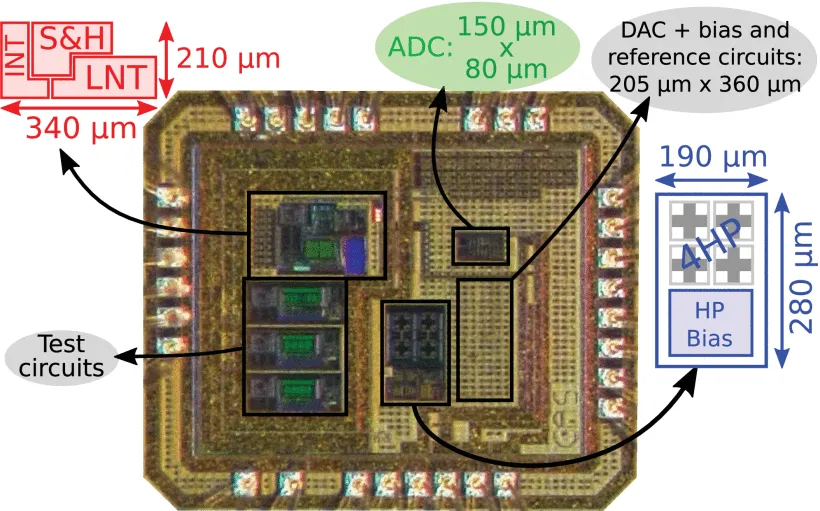

The prototype consists of four hot plates hard-wired in parallel. The overall Hall sensor offset can be decreased by biasing hotplates in different directions. The prototype was fabricated using CMOS technology with thick-oxide devices at 3.3V. Its total size is comparable to the smallest Europractice Mini-ASIC block. A field-programmable gate array makes up the digital circuit.

The proposed Hall sensor readout system provides a digital output and exhibits a measured bandwidth of 410kHz, a very low noise of only 55nT/sqrt(Hz), on a compact active chip area of 0.21mm² and consumes 5.1mA. The prototype shows potential for bandwidth-demanding magnetic current-sensing and high-accuracy magnetic position-sensing applications.